# ECE/CS 552: Data Path and Control

Instructor:Mikko H Lipasti

Fall 2010 University of Wisconsin-Madison

Lecture notes based on set created by Mark Hill.

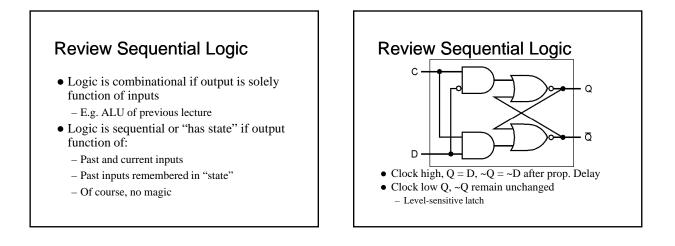

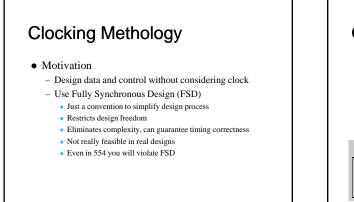

### **Processor Implementation**

- Forecast heart of 552 key to project

- Sequential logic design review (brief)

- Clock methodology (FSD)

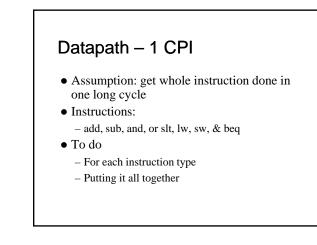

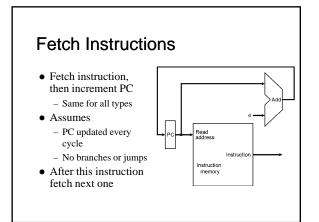

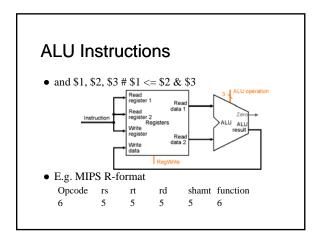

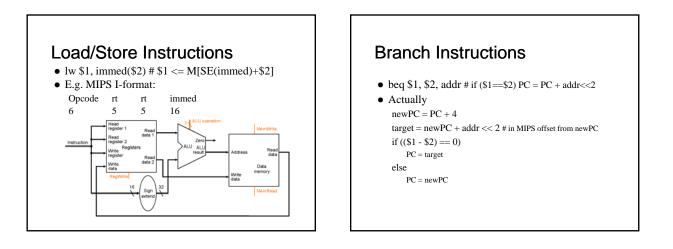

- Datapath 1 CPI

- Single instruction, 2's complement, unsigned

- Control

- Multiple cycle implementation (information only)

- MicroprogrammingExceptions

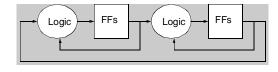

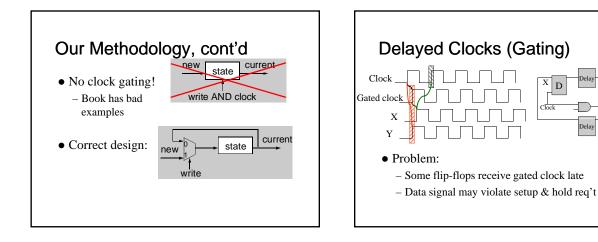

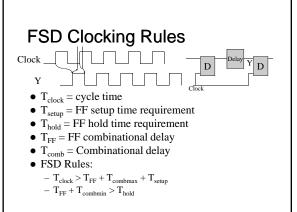

### **Our Methodology**

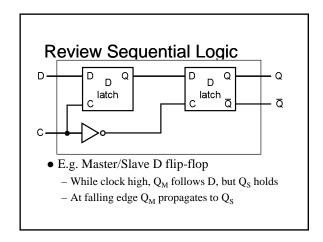

- Only flip-flops

- All on the same edge (e.g. falling)

- All with same clock

- No need to draw clock signals

- All logic finishes in one cycle

D

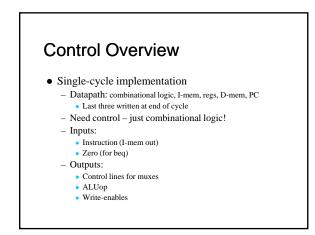

# **Control Overview**

- Fast control

- Divide up work on "need to know" basis

- Logic with fewer inputs is faster

- E.g.

- Global control need not know which ALUop

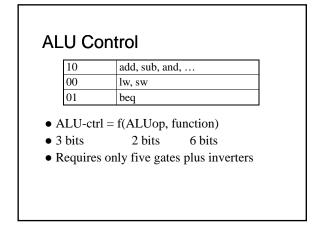

# ALU Control

• Assume ALU uses

| 000    | and                 |

|--------|---------------------|

| 001    | or                  |

| 010    | add                 |

| 110    | sub                 |

| 111    | slt (set less than) |

| others | don't care          |

| Instruction | Operation | Opcode | Function |

|-------------|-----------|--------|----------|

| add         | add       | 000000 | 100000   |

| sub         | sub       | 000000 | 100010   |

| and         | and       | 000000 | 100100   |

| or          | or        | 000000 | 100101   |

| slt         | slt       | 000000 | 101010   |

• ALU-ctrl = f(opcode,function)

# But...don't forget

| Instruction | Operation | Opcode | function |

|-------------|-----------|--------|----------|

| lw          | add       | 100011 | XXXXXX   |

| sw          | add       | 101011 | XXXXXX   |

| beq         | sub       | 000100 | 100010   |

• To simplify ALU-ctrl - ALUop = f(opcode) 2 bits 6 bits

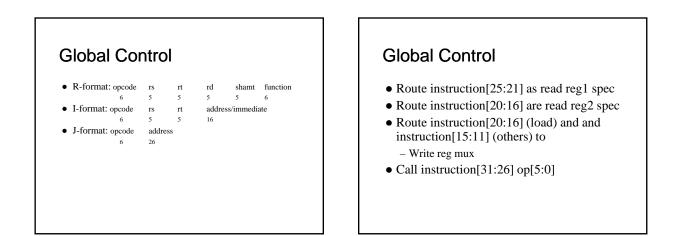

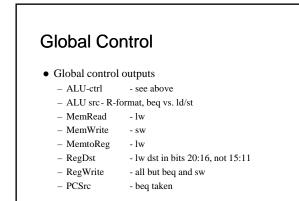

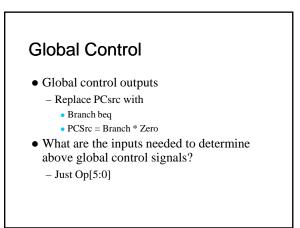

### **Global Control**

| Instruction | Opcode | RegDst | ALUSrc |

|-------------|--------|--------|--------|

| rrr         | 000000 | 1      | 0      |

| lw          | 100011 | 0      | 1      |

| sw          | 101011 | х      | 1      |

| beq         | 000100 | х      | 0      |

| ???         | others | х      | х      |

• RegDst =  $\sim$ Op[0]

• ALUSrc = Op[0]

• RegWrite =  $\sim$ Op[3] \*  $\sim$ Op[2]

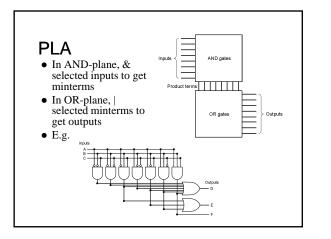

### **Global Control**

- More complex with entire MIPS ISA

- Need more systematic structure

- Want to share gates between control signals

- Common solution: PLA

- MIPS opcode space designed to minimize PLA inputs, minterms, and outputs

- Refer to MIPS Opcode map

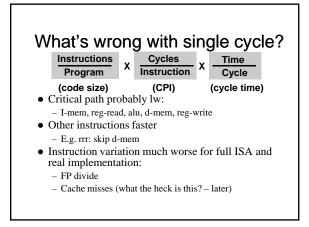

#### • Solution

- Variable clock?

- Too hard to control, design

- Fixed short clock

- Variable cycles per instruction

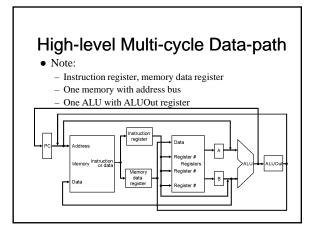

### Multi-cycle Implementation

- Clock cycle = max(i-mem,reg-read+reg-write, ALU, d-mem)

- Reuse combinational logic on different cycles - One memory

- One ALU without other adders

- But

- Control is more complex

- Need new registers to save values (e.g. IR)

- Used again on later cycles

Logic that computes signals is reused

# Comment on busses

- Share wires to reduce #signals – Distributed multiplexor

- Multiple sources driving one bus

- Ensure only one is active!

| Aulti-cycle Steps |             |                                   |

|-------------------|-------------|-----------------------------------|

| Step              | Description | Sample Actions                    |

| IF F              | Fetch       | IR=MEM[PC]                        |

|                   |             | PC=PC+4                           |

| ID De             | Decode      | A=RF(IR[25:21])                   |

|                   |             | B=RF(IR[20:16])                   |

|                   |             | Target=PC+SE(IR[15:0] << 2)       |

| EX F              | Execute     | ALUout = A + SE(IR[15:0]) # lw/sw |

|                   |             | ALUout = A op B # rrr             |

|                   |             | if (A==B) PC = target # beq       |

| Mem M             | Memory      | MEM[ALUout] = B # sw              |

|                   |             | MDR = MEM[ALUout] #lw             |

|                   |             | RF(IR[15:11]) = ALUout # rrr      |

| WB                | Writeback   | Reg(IR[20:16]) = MDR # lw         |

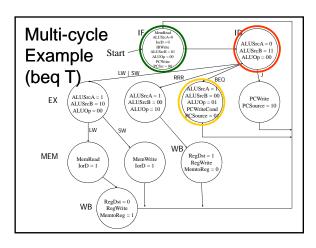

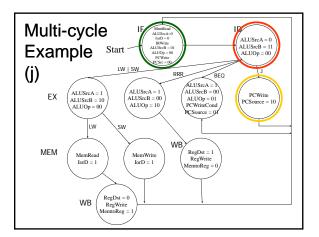

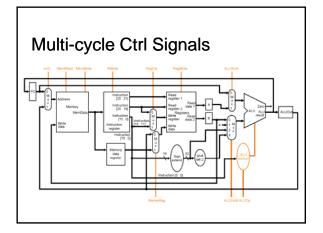

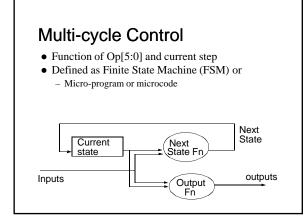

### Finite State Machine (FSM)

- For each state, define:

- Control signals for datapath for this cycle

- Control signals to determine next state

- All instructions start in same IF state

- Instructions terminate by making IF next - After proper PC update, of course

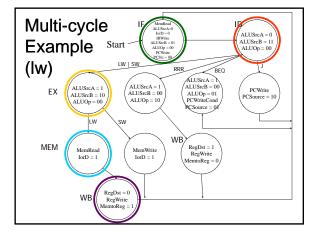

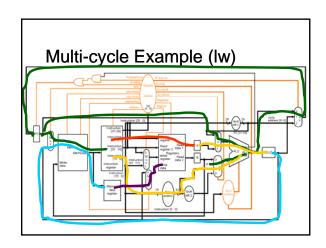

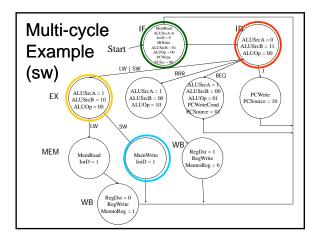

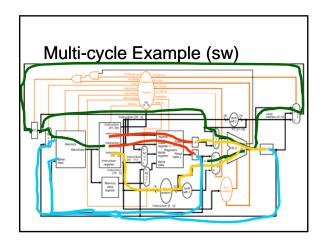

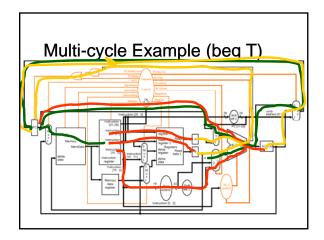

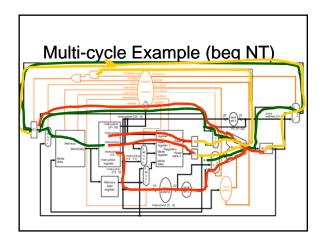

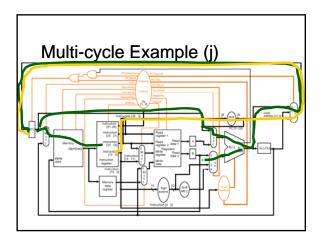

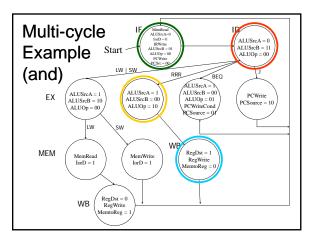

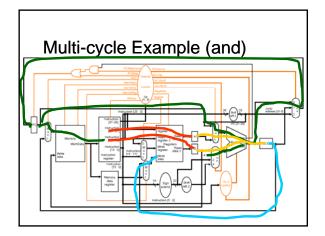

# Multi-cycle Example

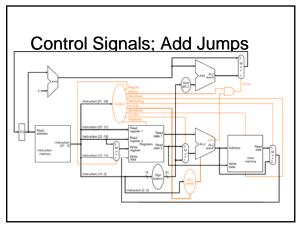

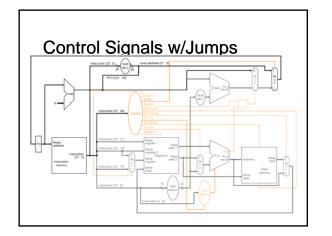

- Datapath (Fig. 5.33 from book) - Will walk *and* \$1, \$2, \$3 through datapath

- Look at control FSM (Fig. 5.42 from book)

- Will walk *and \$1, \$2, \$3* through FSMWill skip

- Repeat for lw, sw, beq taken, beq n-t, j

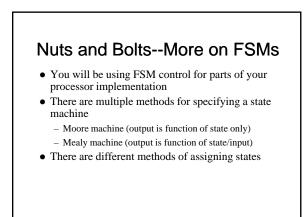

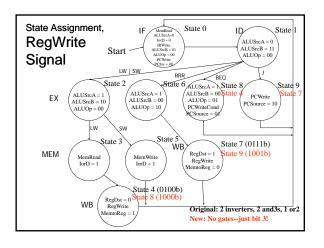

- State assignment is converting logical states to binary representation

- Use ECE 352 methods to build real state machine

- Is state assignment interesting/important?

- Judicious choice of state representation can make next state fcn/output fcn have fewer gates

- Optimal solution is hard, but having intuition is helpful (CAD tools can also help in practice)

### State Assignment--Example

- 10 states in multicycle control FSM

- Each state can have 1 of 16 (2<sup>4</sup>) encodings with "dense" state representation

- Any choice of encoding is fine functionally as long as all states are unique

- Appendix C-26 example: RegWrite signal

# Summary

- Processor implementation

- Datapath

- Control

- Single cycle implementation

- Next: microprogramming

- Remaining slides for reference only